User's Manual

Preliminary

September 15, 2020 Version 0.666

© Copyright International Business Machines Corporation 2010, 2020

Printed in the United States of America

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at <a href="http://www.ibm.com/legal/copytrade.shtml">www.ibm.com/legal/copytrade.shtml</a>.

Intel is a trademark or registered trademark of Intel Corporation or its subsidiaries in the United States and other countries.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this documents, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com®. The IBM semiconductor solutions home page can be found at ibm.com/chips.

Version 0.666 September 15, 2020

### Contents

| List of Figures                                                                            |                           |

|--------------------------------------------------------------------------------------------|---------------------------|

| List of Tables                                                                             | 23                        |

| Revision Log                                                                               |                           |

| About This Book                                                                            |                           |

| Who Should Use This Book                                                                   |                           |

|                                                                                            | • How to Use This Book 31 |

|                                                                                            | • Notation 32             |

|                                                                                            | • Related Publications 33 |

| List of Acronyms and Abbreviations                                                         |                           |

| 1. Overview                                                                                |                           |

| 1.1 A2o Core Key Design Fundamentals                                                       |                           |

| 1.2 A2O core Features                                                                      |                           |

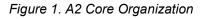

| 1.3 A2O Core Organization                                                                  |                           |

| 1.3.1 Instruction Unit                                                                     |                           |

| 1.3.2 Execution Unit                                                                       | 50                        |

| 1.3.3 Instruction and Data Caches                                                          | 50                        |

| 1.3.3.1 Instruction Cache                                                                  | 50                        |

| 1.3.3.2 Data Cache                                                                         |                           |

| 1.3.4 Memory Management Unit (MMU)                                                         |                           |

| 1.3.5 Timers                                                                               |                           |

| 1.3.6 Debug Facilities                                                                     |                           |

| 1.3.6.1 Debug Modes                                                                        |                           |

| 1.3.6.2 Development Tool Support                                                           |                           |

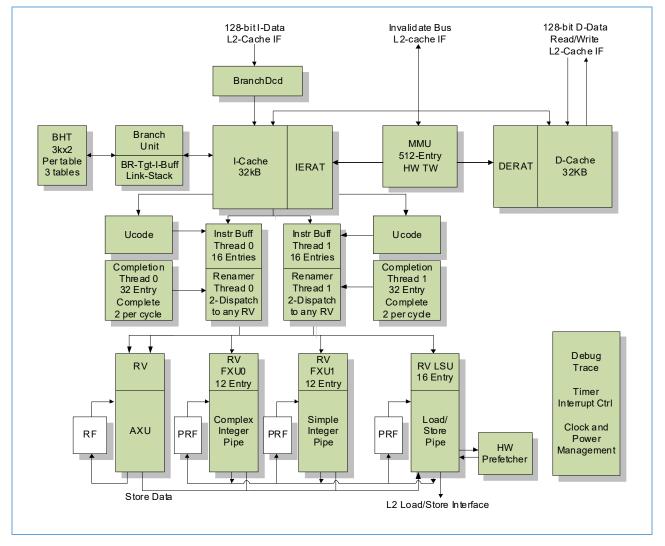

| 1.3.7 Floating-Point Unit Organization                                                     |                           |

| 1.3.7.1 Arithmetic and Load/Store Pipelines<br>1.3.8 IEEE 754 and Architectural Compliance |                           |

| 1.3.8.1 IEEE 754 Compliance                                                                |                           |

| 1.3.9 Floating-Point Unit Implementation                                                   |                           |

| 1.3.9.1 Reciprocal Estimates                                                               |                           |

| 1.3.9.2 Denormalized B Operands                                                            |                           |

| 1.3.9.3 Non-IEEE mode                                                                      |                           |

| 1.3.10 Floating-Point Unit Interfaces                                                      |                           |

| 1.3.10.1 A2 Processor Core Interface                                                       |                           |

| 1.3.10.2 Clock and Power Management Interface                                              |                           |

| 1.4 Core Interfaces                                                                        |                           |

| 1.4.1 System Interface                                                                     |                           |

| 1.4.2 Auxiliary Execution Unit (AXU) Port                                                  |                           |

| 1.4.3 JTAG Port                                                                            | 57                        |

| 2. | CPU Programming Model                                     | 59   |

|----|-----------------------------------------------------------|------|

|    | 2.1 Logical Partitioning                                  | . 59 |

|    | 2.1.1 Overview                                            |      |

|    | 2.2 Storage Addressing                                    | . 60 |

|    | 2.2.1 Storage Operands                                    |      |

|    | 2.2.2 Effective Address Calculation                       |      |

|    | 2.2.2.1 Data Storage Addressing Modes                     |      |

|    | 2.2.2.2 Instruction Storage Addressing Modes              |      |

|    | 2.2.3 Byte Ordering                                       |      |

|    | 2.2.3.1 Structure Mapping Examples                        |      |

|    | 2.2.3.2 Instruction Byte Ordering                         |      |

|    | 2.2.3.3 Data Byte Ordering                                |      |

|    | 2.2.3.4 Byte-Reverse Instructions                         |      |

|    | 2.3 Multithreading                                        |      |

|    | 2.3.1 Thread Identification                               |      |

|    | 2.3.1.1 Thread Identification Register (TIR)              |      |

|    | 2.3.1.2 Processor Identification Register (PIR)           |      |

|    | 2.3.1.3 Guest Processor Identification Register (GPIR)    |      |

|    | 2.3.2 Thread Run State                                    |      |

|    | 2.3.2.1 Thread Stop I/O Pin                               | . 69 |

|    | 2.3.2.2 Thread Control and Status Register (THRCTL)       | . 69 |

|    | 2.3.2.3 Core Configuration Register 0 (CCR0)              | . 69 |

|    | 2.3.2.4 Thread Enable Register (TENS, TENC)               | . 70 |

|    | 2.3.2.5 Thread Enable Status Register (TENSR)             |      |

|    | 2.3.3 Wake On Interrupt                                   | . 72 |

|    | 2.3.3.1 Core Configuration Register 1 (CCR1)              | . 72 |

|    | 2.3.4 Thread Priority                                     |      |

|    | 2.3.4.1 Program Priority Register (PPR32)                 |      |

|    | 2.3.4.2 Instruction Unit Configuration Register 1 (IUCR1) |      |

|    | 2.3.5 Resources Shared between Threads                    |      |

|    | 2.3.6 Shared Resources                                    |      |

|    | 2.3.6.1 Accessing Shared Resources                        |      |

|    | 2.3.7 Duplicated Resources                                |      |

|    | 2.3.8 Pipeline Sharing                                    |      |

|    | 2.3.8.1 Instruction Cache                                 |      |

|    | 2.3.8.2 Instruction Buffer and Decode Dependency          |      |

|    | 2.3.8.3 Instruction Dispatch                              |      |

|    | 2.3.8.4 Instruction Issue                                 |      |

|    | 2.3.8.5 Ram Unit                                          |      |

|    | 2.3.8.6 Microcode Unit                                    |      |

|    | 2.3.8.7 Execution Units                                   |      |

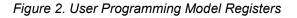

|    | 2.4 Registers                                             |      |

|    | 2.4.1 Register Mapping                                    |      |

|    | 2.4.2 Register Types                                      |      |

|    | 2.4.2.1 General Purpose Registers                         |      |

|    | 2.4.2.2 Special Purpose Registers                         |      |

|    | 2.4.2.3 Condition Register                                |      |

|    | 2.4.2.4 Machine State Register                            |      |

|    | 2.5 32-Bit Mode                                           |      |

|    | 2.5.1 64-Bit Specific Instructions                        | . 82 |

#### A20 Processor

| 2.5.2 32-Bit Instruction Selection                                                | 82     |

|-----------------------------------------------------------------------------------|--------|

| 2.6 Instruction Categories                                                        | 82     |

| 2.7 Instruction Classes                                                           | 84     |

| 2.7.1 Defined Instruction Class                                                   | 84     |

| 2.7.2 Illegal Instruction Class                                                   | 85     |

| 2.7.3 Reserved Instruction Class                                                  | 85     |

| 2.8 Implemented Instruction Set Summary                                           | 85     |

| 2.8.1 Integer Instructions                                                        |        |

| 2.8.1.1 Integer Storage Access Instructions                                       | 86     |

| 2.8.1.2 Integer Arithmetic Instructions                                           | 88     |

| 2.8.1.3 Integer Logical Instructions                                              | 89     |

| 2.8.1.4 Integer Compare Instructions                                              | 89     |

| 2.8.1.5 Integer Trap Instructions                                                 | 89     |

| 2.8.1.6 Integer Rotate Instructions                                               | 90     |

| 2.8.1.7 Integer Shift Instructions                                                | 90     |

| 2.8.1.8 Integer Population Count Instructions                                     |        |

| 2.8.1.9 Integer Select Instruction                                                |        |

| 2.8.1.10 Binary Coded Decimal Assist Instructions                                 |        |

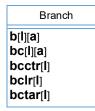

| 2.8.2 Branch Instructions                                                         |        |

| 2.8.3 Processor Control Instructions                                              |        |

| 2.8.3.1 Condition Register Logical Instructions                                   |        |

| 2.8.3.2 Register Management Instructions                                          |        |

| 2.8.3.3 System Linkage Instructions                                               |        |

| 2.8.3.4 Processor Control Instructions                                            |        |

| 2.8.4 Storage Control Instructions                                                |        |

| 2.8.4.1 Cache Management Instructions                                             |        |

| 2.8.4.2 Storage Visibility Instructions                                           |        |

| 2.8.4.3 TLB Management Instructions                                               |        |

| 2.8.4.4 Processor Synchronization Instruction                                     | 94     |

| 2.8.4.5 Load and Reserve and Store Conditional Instructions                       |        |

| 2.8.4.6 Storage Synchronization Instructions                                      | 94     |

| 2.8.4.7 Wait Instruction                                                          |        |

| 2.8.5 Initiate Coprocessor Instructions                                           |        |

| 2.8.5.1 Cache Initialization Instructions                                         |        |

| 2.8.5.2 Debug Instructions                                                        |        |

| 2.9 Branch Processing                                                             |        |

| 2.9.1 Branch Addressing                                                           |        |

| 2.9.2 Branch Instruction BI Field                                                 |        |

| 2.9.3 Branch Instruction BO Field                                                 |        |

| 2.9.4 Branch Prediction                                                           |        |

| 2.9.4.1 Branch Decoder                                                            |        |

| 2.9.4.2 Branch Direction Prediction                                               |        |

| 2.9.4.4 Dynamic Hardware Prediction                                               |        |

| 2.9.4.5 Performance Model Dynamic Predictor                                       |        |

| 2.9.4.5 Performance Model Dynamic Predictor                                       |        |

| gshare counter used during prediction is updated. The other gshare counter is not | ly the |

| updated.Bimodal Branch History                                                    | 101    |

| 2.9.4.7 Bimodal Branch History                                                    |        |

| 2.9.5 Branch Control Registers                                                    |        |

| 2.7.0 Branen control (Capitero                                                    | . 102  |

| 2.9.5.1 Link Register (LR)                                       |                   |

|------------------------------------------------------------------|-------------------|

| 2.9.5.2 Count Register (CTR)                                     |                   |

| 2.9.5.3 Condition Register (CR)                                  |                   |

| 2.9.5.4 Target Address Register                                  |                   |

| 2.10 Integer Processing                                          |                   |

| 2.10.1 General Purpose Registers (GPRs)                          |                   |

| 2.10.2 Integer Exception Register (XER)                          |                   |

| 2.10.2.1 Summary Overflow (SO) Field                             |                   |

| 2.10.2.2 Overflow (OV) Field                                     |                   |

| 2.10.2.3 Carry (CA) Field                                        |                   |

| 2.10.2.4 Transfer Byte Count (TBC) Field                         |                   |

| 2.11 Processor Control                                           |                   |

| 2.11.1 Special Purpose Registers General (SPRG0–SPRG8)           |                   |

| 2.11.2 External Process ID Load Context (EPLC) Register          |                   |

| 2.11.3 External Process ID Store Context (EPSC) Register         |                   |

| 2.12 Privileged Modes                                            |                   |

| 2.12.1 Privileged Instructions                                   |                   |

| 2.12.1.1 Cache Locking Instructions                              |                   |

| 2.12.2 Privileged SPRs                                           | 118               |

| 2.13 Speculative Accesses                                        | 118               |

| 2.14 Synchronization                                             | 118               |

| 2.14.1 Context Synchronization                                   |                   |

| 2.14.2 Execution Synchronization                                 |                   |

| 2.14.3 Storage Ordering and Synchronization                      | 120               |

| 2.15 Software Transactional Memory Acceleration                  | . 121             |

| 2.15.1 Summary                                                   | . 121             |

| 2.15.2 Implementation                                            |                   |

| 2.15.2.1 L1 D-Cache                                              |                   |

| 2.15.3 Watch Operation Ordering Requirements                     |                   |

| 2.15.4 Impact on Existing Software                               | 122               |

|                                                                  |                   |

| 3. FU Programming Model                                          |                   |

| 3.1 Storage Addressing                                           |                   |

| 3.1.1 Storage Operands                                           |                   |

| 3.1.2 Effective Address Calculation                              |                   |

| 3.1.3 Data Storage Addressing Modes                              | 124               |

| 3.2 Floating-Point Exceptions                                    | 125               |

| 3.3 Floating-Point Registers                                     |                   |

| 3.3.1 Register Types                                             | 126               |

| 3.3.1.1 Floating-Point Registers (FPR0–FPR31)                    |                   |

| 3.3.1.2 Floating-Point Status and Control Register (FPSCR)       |                   |

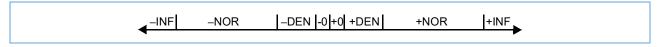

| 3.4 Floating-Point Data Formats                                  |                   |

| 3.4.1 Value Representation                                       |                   |

| 3.4.2 Binary Floating-Point Numbers                              |                   |

| 3.4.2.1 Normalized Numbers                                       | 131               |

| 3.4.2.2 Denormalized Numbers                                     |                   |

|                                                                  | 132               |

| 3.4.2.3 Zero Values                                              | 132<br>132        |

| 3.4.2.3 Zero Values<br>3.4.3 Infinities<br>3.4.3.1 Not a Numbers | 132<br>132<br>132 |

#### A20 Processor

| 3.4.4 Sign of Result                                                    | 133        |

|-------------------------------------------------------------------------|------------|

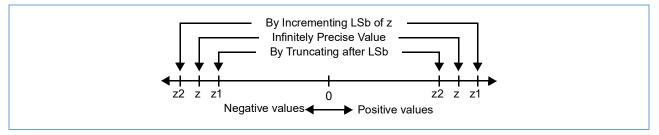

| 3.4.5 Normalization and Denormalization                                 |            |

| 3.4.6 Data Handling and Precision                                       |            |

| 3.4.7 Rounding                                                          | 135        |

| 3.5 Floating-Point Execution Models                                     |            |

| 3.5.1 Execution Model for IEEE Operations                               |            |

| 3.5.2 Execution Model for Multiply-Add Type Instructions                |            |

| 3.6 Floating-Point Instructions                                         |            |

| 3.6.1 Instructions by Category                                          |            |

| 3.6.2 Load and Store Instructions                                       |            |

| 3.6.3 Floating-Point Store Instructions                                 |            |

| 3.6.4 Floating-Point Move Instructions                                  |            |

| 3.6.5 Floating-Point Arithmetic Instructions                            |            |

| 3.6.5.1 Floating-Point Multiply-Add Instructions                        | 145        |

| 3.6.6 Floating-Point Rounding and Conversion Instructions               |            |

| 3.6.7 Floating-Point Compare Instructions                               |            |

| 3.6.8 Floating-Point Status and Control Register Instructions           |            |

|                                                                         |            |

| 4. Initialization                                                       |            |

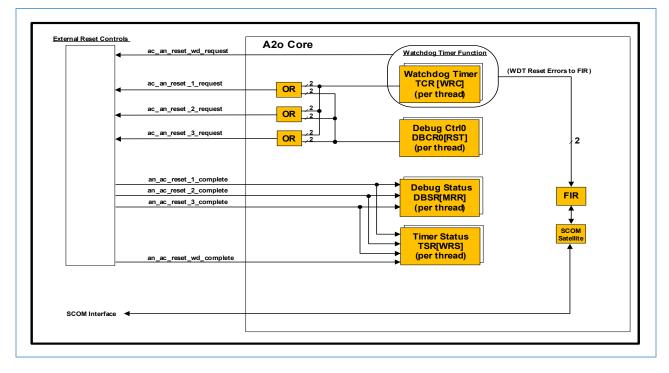

| 4.1 Core Reset                                                          |            |

| 4.2 A2 Core State After Reset                                           |            |

| 4.3 Core Reset Request and Status Signals                               |            |

| 4.3.1 Core Reset Requests                                               |            |

| 4.3.1.1 From Debug                                                      |            |

| 4.3.1.2 From Watchdog Timer                                             |            |

| 4.3.2 Reset Request Status                                              |            |

| 4.3.2.1 Debug Facility Reset Status                                     |            |

| 4.3.2.2 Timer Facility Reset Status                                     |            |

| 4.4 Initialization Software Requirements                                | 152        |

| E Instruction and Data Cashas                                           | 450        |

| 5. Instruction and Data Caches                                          |            |

| 5.1 Data Cache Array Organization and Operation                         |            |

| 5.2 Instruction Cache Array Organization and Operation                  |            |

| 5.3 Cache Line Replacement Policy                                       |            |

| 5.4 Instruction Cache Controller                                        |            |

| 5.4.1 ICC Operations                                                    |            |

| 5.4.2 Instruction Cache Coherency                                       |            |

| 5.4.2.1 Self-Modifying Code                                             |            |

| 5.4.2.2 Instruction Cache Synonyms                                      |            |

| 5.4.3 Instruction Cache Control and Debug                               |            |

| 5.4.3.1 Instruction Cache Management and Debug Instruction Summary      |            |

| 5.4.3.2 Instruction Cache Parity Operations                             |            |

| 5.4.3.3 Simulating Instruction Cache Parity Errors for Software Testing |            |

| 5.5 Data Cache Controller                                               |            |

| 5.5.1 DCC Operations                                                    |            |

| 5.5.1.1 Load and Store Alignment                                        |            |

| 5.5.1.2 Load Operations<br>5.5.1.3 Store Operations                     |            |

| 5.5.1.4 Data Read and Instruction Fetch Interface Requests              | 100<br>160 |

| 5.5.1.4 Data Neau and Instruction Fetch Interface Requests              | тоо        |

| 5.5.1.5 Data Write Interface Requests                                         |     |

|-------------------------------------------------------------------------------|-----|

| 5.5.1.6 Storage Access Ordering                                               |     |

| 5.5.2 Data Cache Coherency                                                    |     |

| 5.5.3 Data Cache Control                                                      |     |

| 5.5.3.1 Data Cache Management Instruction Summary                             |     |

| 5.5.3.2 dcbt and dcbtst Operation                                             |     |

| 5.5.3.3 Cache Locking Mechanisms                                              |     |

| 5.5.3.4 Data Cache Parity Operations                                          |     |

| 5.5.3.5 Simulating Data Cache Parity Errors for Software Testing              |     |

| 5.5.3.6 Data Cache Disable                                                    |     |

| 6. Memory Management                                                          | 160 |

|                                                                               |     |

| 6.1 MMU Overview<br>6.1.1 Support for Power ISA MMU Architecture              |     |

|                                                                               |     |

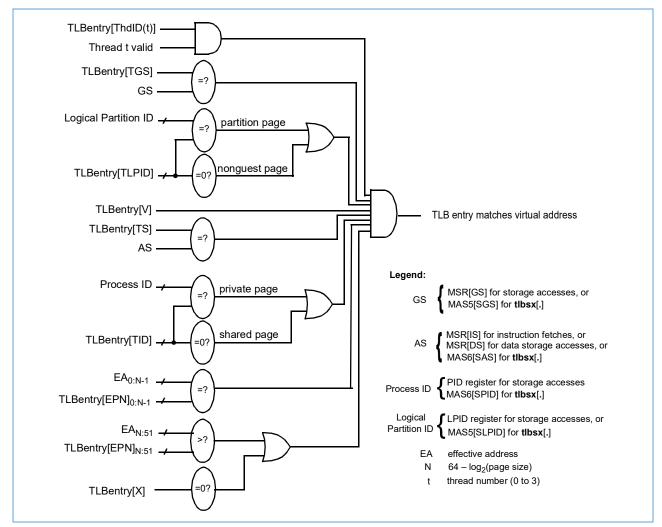

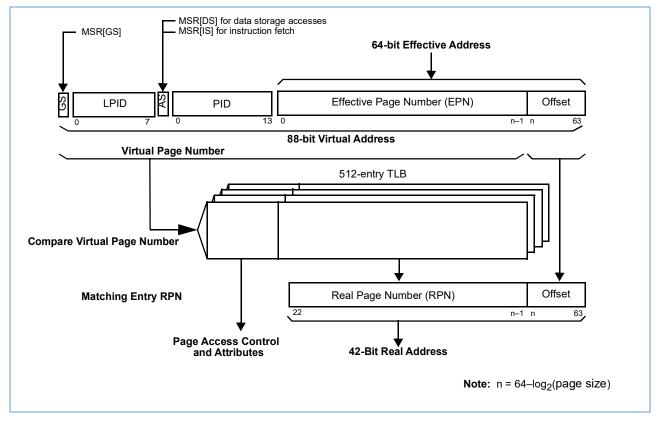

| 6.2 Page Identification                                                       |     |

| 6.2.1 Virtual Address Formation                                               |     |

| 6.2.2 Address Space Identifier Convention                                     |     |

| 6.2.3 Exclusion Range (X-bit) Operation                                       |     |

| 6.2.4 TLB Match Process                                                       |     |

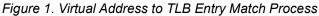

| 6.3 Address Translation                                                       |     |

| 6.4 Access Control                                                            |     |

| 6.4.1 Execute Access                                                          |     |

| 6.4.2 Write Access                                                            |     |

| 6.4.3 Read Access                                                             |     |

| 6.4.4 Access Control Applied to Cache Management Instructions                 |     |

| 6.5 Storage Attributes                                                        |     |

| 6.5.1 Write-Through (W)                                                       |     |

| 6.5.2 Caching Inhibited (I)                                                   |     |

| 6.5.3 Memory Coherence Required (M)                                           |     |

| 6.5.4 Guarded (G)                                                             |     |

| 6.5.5 Endian (E)                                                              |     |

| 6.5.6 User-Definable (U0–U3)                                                  |     |

| 6.5.7 Supported Storage Attribute Combinations                                |     |

| 6.5.8 Aliasing                                                                |     |

| 6.6 Translation Lookaside Buffer                                              |     |

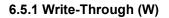

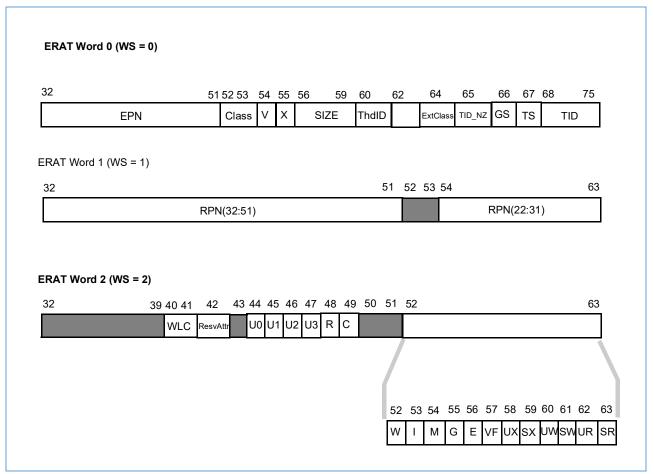

| 6.7 Effective to Real Address Translation Arrays                              |     |

| 6.7.1 ERAT Context Synchronization                                            |     |

| 6.7.2 ERAT Reset Behavior                                                     |     |

| 6.7.3 Atomic Update of ERAT Entries                                           |     |

| 6.7.4 ERAT LRU Round-Robin Replacement Mode                                   |     |

| 6.7.5 ERAT LRU Replacement Watermark                                          |     |

| 6.7.6 ERAT (TLB Lookaside Information) Coherency and Back-Invalidation        |     |

| 6.7.7 ERAT External PID (EPID) Context and Instruction Dependencies           |     |

| 6.8 Logical to Real Address Translation Array (Category E.HV.LRAT)            |     |

| 6.9 TLB Management Instructions (Architected)                                 |     |

| 6.9.1 TLB Read and Write Instructions ( <b>tlbre</b> and <b>tlbwe</b> )       |     |

| 6.9.2 TLB Search Instruction ( <b>tlbsx[.]</b> )                              |     |

| 6.9.3 TLB Search and Reserve Instruction (tlbsrx.)                            |     |

| 6.9.4 TLB Invalidate Virtual Address (Indexed) Instruction ( <b>tlbivax</b> ) | 200 |

| 6.9.5 TLB Invalidate Local (Indexed) Instruction ( <b>tlbilx</b> )                         |     |

|--------------------------------------------------------------------------------------------|-----|

| 6.9.6 TLB Sync Instruction ( <b>tlbsync</b> )                                              | 202 |

| 6.10 ERAT Management Instructions (Non-Architected)                                        | 203 |

| 6.10.1 ERAT Read and Write Instructions (eratre and eratwe)                                | 203 |

| 6.10.2 ERAT Search Instruction (eratsx[.])                                                 | 204 |

| 6.10.3 ERAT Invalidate Virtual Address (Indexed) Instruction ( <b>erativax</b> )           | 205 |

| 6.10.4 ERAT Invalidate Local (Indexed) Instruction ( <b>eratilx</b> )                      | 208 |

| 6.11 32-Bit Mode Memory Management Behavior                                                | 208 |

| 6.11.1 32-Bit Mode TLB Read and Write Instructions (tlbre and tlbwe)                       | 209 |

| 6.11.2 32-Bit Mode TLB Search Instruction (tlbsx[.])                                       | 209 |

| 6.11.3 32-Bit Mode TLB Search and Reserve Instruction ( <b>tlbsrx.</b> )                   | 209 |

| 6.11.4 32-Bit Mode TLB Invalidate Virtual Address (Indexed) Instruction ( <b>tlbivax</b> ) | 210 |

| 6.11.5 32-Bit Mode TLB Invalidate Local (Indexed) Instruction ( <b>tlbilx</b> )            | 210 |

| 6.11.6 32-Bit Mode TLB Sync Instruction ( <b>tlbsync</b> )                                 | 210 |

| 6.11.7 32-Bit Mode ERAT Read and Write Instructions (eratre and eratwe)                    | 210 |

| 6.11.8 32-Bit Mode ERAT Search Instruction (eratsx[.])                                     | 211 |

| 6.11.9 32-Bit Mode ERAT Invalidate Virtual Address (Indexed) Instruction (erativax)        | 211 |

| 6.11.10 32-Bit Mode ERAT Invalidate Local (Indexed) Instruction ( <b>eratilx</b> )         | 212 |

| 6.12 Page Reference and Change Status Management                                           | 212 |

| 6.13 TLB and ERAT Parity Operations                                                        |     |

| 6.13.1 Parity Errors Generated from <b>tlbre</b> or <b>eratre</b>                          |     |

| 6.13.2 Simulating TLB and ERAT Parity Errors for Software Testing                          |     |

| 6.14 ERAT-Only Mode Operation                                                              |     |

| 6.15 TLB Reservations and TLB Write Conditional (Category E.TWC)                           |     |

| 6.16 Hardware Page Table Walking (Category E.PT)                                           |     |

| 6.16.1 Searching the TLB for Direct and Indirect Entries                                   |     |

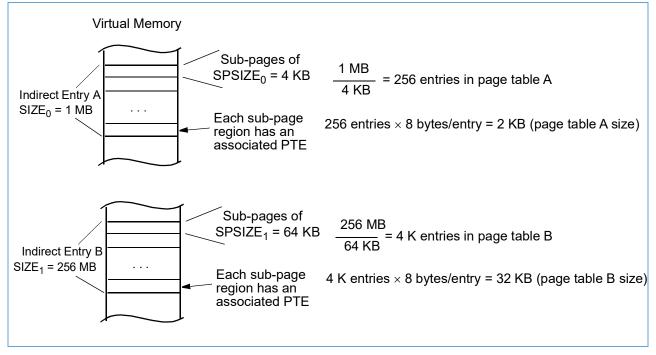

| 6.16.2 Indirect TLB Entry Page and Sub-Page Sizes                                          |     |

| 6.16.3 Hardware Page Table Entry Format                                                    |     |

| 6.16.4 Calculation of Hardware Page Table Entry Real Address                               |     |

| 6.16.5 Hardware Page Table Errors and Exceptions                                           |     |

| 6.16.6 Hardware Page Table Storage Control Attributes                                      |     |

| 6.16.7 TLB Update After Hardware Page Table Translation                                    |     |

|                                                                                            |     |

| 6.17 Storage Control Registers (Architected)                                               |     |

| 6.17.1 Process ID Register (PID)                                                           |     |

| 6.17.2 Logical Partition ID Register (LPIDR)                                               |     |

| 6.17.3 External PID Load Context (EPLC) Register                                           |     |

| 6.17.4 External PID Store Context (EPSC) Register                                          |     |

| 6.17.5 MMU Assist Register 0 (MAS0)<br>6.17.6 MMU Assist Register 1 (MAS1)                 |     |

|                                                                                            |     |

| 6.17.7 MMU Assist Register 2 (MAS2)<br>6.17.8 MMU Assist Register 2 Upper (MAS2U)          |     |

|                                                                                            |     |

| 6.17.9 MMU Assist Register 3 (MAS3)<br>6.17.10 MMU Assist Register 4 (MAS4)                | 23/ |

| 6.17.11 MMU Assist Register 5 (MAS5)                                                       |     |

|                                                                                            |     |

| 6.17.12 MMU Assist Register 6 (MAS6)<br>6.17.13 MMU Assist Register 7 (MAS7)               |     |

| 6.17.14 MMU Assist Register 7 (MAS7)                                                       |     |

|                                                                                            |     |

| 6.17.15 MAS0_MAS1 Register                                                                 |     |

| 6.17.16 MAS5_MAS6 Register                                                                 |     |

| 6.17.17 MAS7_MAS3 Register                                                                 | Z40 |

| _   |       | -    |       |

|-----|-------|------|-------|

| Drc | elin  | \in' | 2 F1/ |

| гіе | ;,,,, |      | aı v  |

|     |       |      |       |

| 6.17.18 MAS8_MAS1 Register                                  | 247 |

|-------------------------------------------------------------|-----|

| 6.17.19 MMU Configuration Register (MMUCFG)                 | 248 |

| 6.17.20 MMU Control and Status Register 0 (MMUCSR0)         |     |

| 6.17.21 TLB 0 Configuration Register (TLB0CFG)              | 250 |

| 6.17.22 TLB 0 Page Size Register (TLB0PS)                   | 252 |

| 6.17.23 LRAT Configuration Register (LRATCFG)               | 253 |

| 6.17.24 LRAT Page Size Register (LRATPS)                    | 254 |

| 6.17.25 Embedded Page Table Configuration Register (EPTCFG) |     |

| 6.17.26 Logical Page Exception Register (LPER)              | 257 |

| 6.17.27 Logical Page Exception Register Upper (LPERU)       | 258 |

| 6.17.28 MAS Register Update Summary                         |     |

| 6.18 Storage Control Registers (Non-Architected)            |     |

| 6.18.1 Memory Management Unit Control Register 0 (MMUCR0)   | 261 |

| 6.18.2 Memory Management Unit Control Register 1 (MMUCR1)   |     |

| 6.18.3 Memory Management Unit Control Register 2 (MMUCR2)   |     |

| 6.18.4 Memory Management Unit Control Register 3 (MMUCR3)   | 274 |

|                                                             |     |

| 7. CPU Interrupts and Exceptions                            | 277 |

| 7.1 Overview                                                | 277 |

| 7.2 Directed Interrupts                                     | 277 |

| 7.3 Interrupt Classes                                       | 278 |

| 7.3.1 Asynchronous Interrupts                               |     |

| 7.3.2 Synchronous Interrupts                                | 278 |

| 7.3.2.1 Synchronous, Precise Interrupts                     |     |

| 7.3.2.2 Synchronous, Imprecise Interrupts                   | 279 |

| 7.3.3 Critical and Noncritical Interrupts                   | 280 |

| 7.3.4 Machine Check Interrupts                              | 280 |

| 7.4 Interrupt Processing                                    | 281 |

| 7.4.1 Partially Executed Instructions                       | 283 |

| 7.5 Interrupt Processing Registers                          | 284 |

| 7.5.1 Register Mapping                                      | 285 |

| 7.5.2 Machine State Register (MSR)                          | 285 |

| 7.5.3 Machine State Register Protect (MSRP)                 | 287 |

| 7.5.4 Embedded Processor Control Register (EPCR)            |     |

| 7.5.5 Save/Restore Register 0 (SRR0)                        |     |

| 7.5.6 Save/Restore Register 1 (SRR1)                        |     |

| 7.5.7 Guest Save/Restore Register 0 (GSRR0)                 |     |

| 7.5.8 Guest Save/Restore Register 1 (GSRR1)                 |     |

| 7.5.9 Critical Save/Restore Register 0 (CSRR0)              |     |

| 7.5.10 Critical Save/Restore Register 1 (CSRR1)             |     |

| 7.5.11 Machine Check Save/Restore Register 0 (MCSRR0)       |     |

| 7.5.12 Machine Check Save/Restore Register 1 (MCSRR1)       |     |

| 7.5.13 Data Exception Address Register (DEAR)               |     |

| 7.5.14 Guest Data Exception Address Register (GDEAR)        |     |

| 7.5.15 Interrupt Vector Prefix Register (IVPR)              |     |

| 7.5.16 Guest Interrupt Vector Prefix Register (GIVPR)       |     |

| 7.5.17 Exception Syndrome Register (ESR)                    |     |

| 7.5.18 Guest Exception Syndrome Register (GESR)             |     |

| 7.5.19 Machine Check Status Register (MCSR)                 |     |

#### A20 Processor

| 7.6 Interrupt Definitions                                                             |     |

|---------------------------------------------------------------------------------------|-----|

| 7.6.1 Critical Input Interrupt                                                        | 309 |

| 7.6.2 Machine Check Interrupt                                                         |     |

| 7.6.2.1 Machine Check Status Register (MCSR)                                          |     |

| 7.6.3 Data Storage Interrupt                                                          |     |

| 7.6.4 Instruction Storage Interrupt                                                   |     |

| 7.6.5 External Input Interrupt                                                        | 319 |

| 7.6.6 Alignment Interrupt                                                             |     |

| 7.6.7 Program Interrupt                                                               |     |

| 7.6.8 Floating-Point Unavailable Interrupt                                            | 325 |

| 7.6.9 System Call Interrupt                                                           |     |

| 7.6.10 Auxiliary Processor Unavailable Interrupt                                      | 326 |

| 7.6.11 Decrementer Interrupt                                                          |     |

| 7.6.12 Guest Decrementer Interrupt                                                    | 326 |

| 7.6.13 Fixed-Interval Timer Interrupt                                                 |     |

| 7.6.14 Guest Fixed-Interval Timer Interrupt                                           |     |

| 7.6.15 Watchdog Timer Interrupt                                                       | 328 |

| 7.6.16 Guest Watchdog Timer Interrupt                                                 | 328 |

| 7.6.17 Data TLB Error Interrupt                                                       | 329 |

| 7.6.18 Instruction TLB Error Interrupt                                                |     |

| 7.6.19 Vector Unavailable Interrupt                                                   | 331 |

| 7.6.20 Debug Interrupt                                                                | 331 |

| 7.6.21 Processor Doorbell Interrupt                                                   | 335 |

| 7.6.22 Processor Doorbell Critical Interrupt                                          | 336 |

| 7.6.23 Guest Processor Doorbell Interrupt                                             | 336 |

| 7.6.24 Guest Processor Doorbell Critical Interrupt                                    | 337 |

| 7.6.25 Guest Processor Doorbell Machine Check Interrupt                               | 337 |

| 7.6.26 Embedded Hypervisor System Call Interrupt                                      | 338 |

| 7.6.27 Embedded Hypervisor Privilege Interrupt                                        | 338 |

| 7.6.28 LRAT Error Interrupt                                                           | 339 |

| 7.6.29 User Decrementer Interrupt                                                     | 340 |

| 7.6.30 Performance Monitor Interrupt                                                  | 340 |

| 7.7 Processor Messages                                                                | 341 |

| 7.7.1 Processor Message Handling and Filtering                                        |     |

| 7.7.2 Doorbell Message Filtering                                                      |     |

| 7.7.3 Doorbell Critical Message Filtering                                             | 343 |

| 7.7.4 Guest Doorbell Message Filtering                                                | 344 |

| 7.7.5 Guest Doorbell Critical Message Filtering                                       |     |

| 7.7.6 Guest Doorbell Machine Check Message Filtering                                  | 345 |

| 7.8 Interrupt Ordering and Masking                                                    |     |

| 7.8.1 Interrupt Ordering Software Requirements                                        |     |

| 7.8.2 Interrupt Order                                                                 |     |

| 7.9 Exception Priorities                                                              |     |

| 7.9.1 Exception Priorities for Integer Load, Store, and Cache Management Instructions |     |

| 7.9.2 Exception Priorities for Floating-Point Load and Store Instructions             |     |

| 7.9.3 Exception Priorities for Floating-Point Instructions (Other)                    |     |

| 7.9.4 Exception Priorities for Privileged Instructions                                |     |

| 7.9.5 Exception Priorities for Trap Instructions                                      |     |

| 7.9.6 Exception Priorities for System Call Instruction                                |     |

| 7.9.7 Exception Priorities for Branch Instructions                                    |     |

|                                                                                       | 000 |

| _  |      | -   |       |

|----|------|-----|-------|

| D٢ | ıila | mir | nary  |

|    | CIII |     | iai y |

|    | 7.9.8 Exception Priorities for Return From Interrupt Instructions       |     |

|----|-------------------------------------------------------------------------|-----|

|    | 7.9.9 Exception Priorities for Reserved Instructions                    |     |

|    | 7.9.10 Exception Priorities for All Other Instructions                  |     |

|    |                                                                         |     |

| 8. | FU Interrupts and Exceptions                                            | 355 |

|    | 8.1 Floating-Point Exceptions                                           |     |

|    | 8.2 Exceptions List                                                     |     |

|    | 8.3 Floating-Point Interrupts                                           |     |

|    | 8.3.1 Floating-Point Unavailable Interrupt                              |     |

|    | 8.3.2 Floating-Point Assist Interrupt                                   |     |

|    | 8.4 Floating-Point Exception Behavior                                   |     |

|    | 8.4.1 Invalid Operation Exception                                       |     |

|    | 8.4.1.1 Action                                                          |     |

|    | 8.4.2 Zero Divide Exception                                             |     |

|    | 8.4.2.1 Action                                                          |     |

|    | 8.4.3 Overflow Exception                                                |     |

|    | 8.4.3.1 Action                                                          |     |

|    | 8.4.4 Underflow Exception                                               |     |

|    | 8.4.4.1 Action                                                          |     |

|    | 8.4.5 Inexact Exception                                                 |     |

|    | 8.4.5.1 Action                                                          |     |

|    | 8.5 Exception Priorities for Floating-Point Load and Store Instructions |     |

|    | 8.6 Exception Priorities for Other Floating-Point Instructions          |     |

|    | 8.7 QNaN                                                                |     |

|    | 8.8 Updating FPRs on Exceptions                                         |     |

|    | 8.9 Floating-Point Status and Control Register (FPSCR)                  |     |

|    | 8.10 Updating the Condition Register                                    |     |

|    | 8.10.1 Condition Register (CR)                                          |     |

|    | 8.10.2 Updating CR Fields                                               |     |

|    | 8.10.3 Generation of QNaN Results                                       |     |

|    |                                                                         |     |

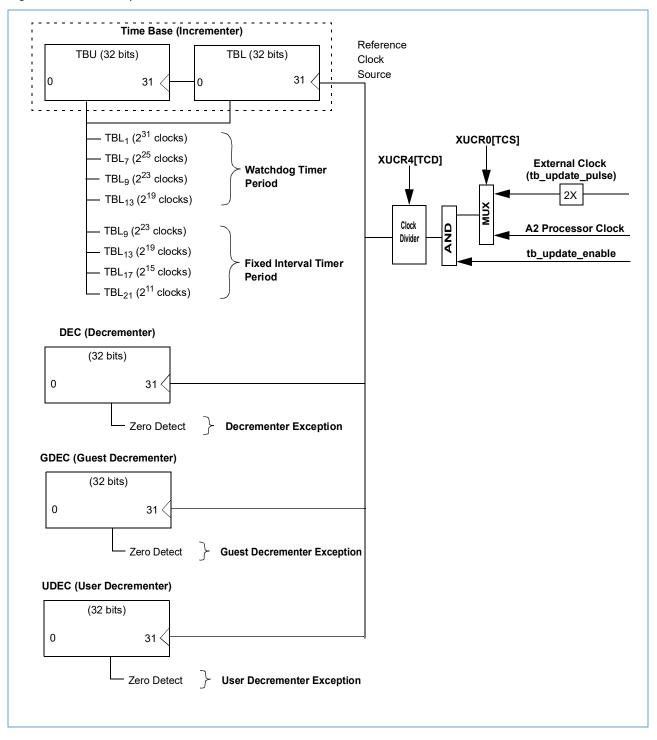

| 9. | Timer Facilities                                                        |     |

|    | 9.1 Time Base                                                           |     |

|    | 9.1.1 Reading the Time Base                                             |     |

|    | 9.1.2 Writing the Time Base                                             |     |

|    | 9.2 Decrementer (DEC)                                                   |     |

|    | 9.3 Guest Decrementer (GDEC)                                            |     |

|    | 9.4 User Decrementer (UDEC)                                             |     |

|    | 9.5 Fixed Interval Timer (FIT)                                          |     |

|    | 9.6 Guest Fixed Interval Timer (GFIT)                                   |     |

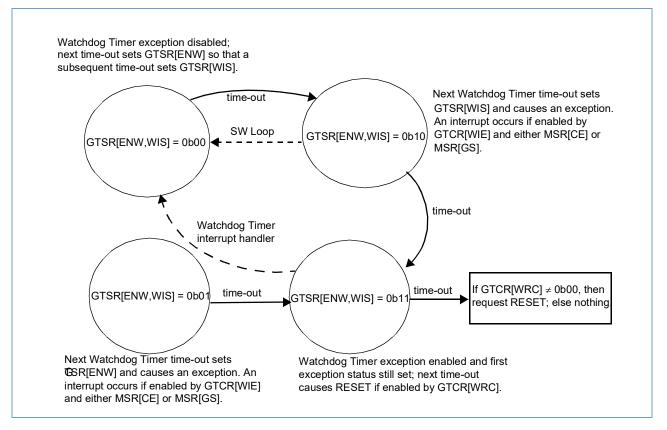

|    | 9.7 Watchdog Timer                                                      |     |

|    | 9.8 Guest Watchdog Timer                                                |     |

|    | 9.9 Timer Control Register (TCR)                                        |     |

|    | 9.10 Guest Timer Control Register (GTCR)                                |     |

|    | 9.11 Timer Status Register (TSR)                                        |     |

|    | 9.12 Guest Timer Status Register (GTSR)                                 |     |

|    | 9.13 Freezing the Timer Facilities                                      |     |

|    | 9.14 Selection of the Timer Clock Source                                |     |

|    |                                                                         |     |

|     | 9.15 Selecting the Timer Clock Frequency Divide Value                                                  | . 386 |

|-----|--------------------------------------------------------------------------------------------------------|-------|

|     | 9.16 Synchronizing Timers Across Multiple Cores                                                        |       |

|     |                                                                                                        |       |

| 10. | Debug Facilities                                                                                       | 389   |

|     | 10.1 Implications of Hypervisor on Debug Controls                                                      | . 389 |

|     | 10.2 Support for Development Tools                                                                     | . 389 |

|     | 10.3 Debug Modes                                                                                       | . 389 |

|     | 10.3.1 Internal Debug Mode                                                                             | . 390 |

|     | 10.3.2 External Debug Mode                                                                             | . 390 |

|     | 10.3.3 Trace Debug Mode                                                                                | . 391 |

|     | 10.4 Debug Events                                                                                      | . 392 |

|     | 10.4.1 Instruction Address Compare (IAC) Debug Event                                                   |       |

|     | 10.4.1.1 IAC Debug Event Fields                                                                        |       |

|     | 10.4.1.2 IAC Debug Event Processing                                                                    |       |

|     | 10.4.2 Data Address Compare (DAC) Debug Event                                                          |       |

|     | 10.4.2.1 DAC Debug Event Fields                                                                        |       |

|     | 10.4.2.2 DAC Debug Event Processing                                                                    |       |

|     | 10.4.2.3 DAC Debug Events Applied to Instructions that Result in Multiple Storage Accesse 397          | es    |

|     | 10.4.2.4 DAC Debug Events Applied to Various Instruction Types                                         |       |

|     | 10.4.3 Data Value Compare (DVC) Debug Event                                                            |       |

|     | 10.4.3.1 DVC Debug Event Fields                                                                        |       |

|     | 10.4.3.2 DVC Debug Event Processing                                                                    |       |

|     | 10.4.3.3 DVC Debug Events Applied to Instructions that Result in Multiple Storage Accesse 400          | es    |

|     | 10.4.3.4 DVC Debug Events Applied to Various Instruction Types                                         | . 401 |

|     | 10.4.3.5 DVC Debug Events Applied to Floating-Point Loads and Stores                                   | . 401 |

|     | 10.4.4 Instruction Complete (ICMP) Debug Event                                                         |       |

|     | 10.4.5 Branch Taken (BRT) Debug Event                                                                  |       |

|     | 10.4.6 Trap (TRAP) Debug Event                                                                         |       |

|     | 10.4.7 Return (RET) Debug Event                                                                        |       |

|     | 10.4.8 Interrupt (IRPT) Debug Event                                                                    |       |

|     | 10.4.9 Unconditional Debug Event (UDE)                                                                 |       |

|     | 10.4.10 Instruction Value Compare (IVC) Debug Event                                                    |       |

|     | 10.4.11 Debug Event Summary                                                                            |       |

|     | 10.5 Debug Reset                                                                                       |       |

|     | 10.6 Debug Timer Freeze                                                                                |       |

|     | 10.7 Debug Registers                                                                                   | . 405 |

|     | 10.7.1 Debug Control Register 0 (DBCR0)                                                                |       |

|     | 10.7.2 Debug Control Register 1 (DBCR1)                                                                |       |

|     | 10.7.3 Debug Control Register 2 (DBCR2)                                                                |       |

|     | 10.7.4 Debug Control Register 3 (DBCR3)                                                                |       |

|     | 10.7.5 Debug Status Register (DBSR)                                                                    | . 412 |

|     | 10.7.6 Debug Status Register Write Register (DBSRWR)                                                   |       |

|     | 10.7.7 Instruction Address Compare Registers (IAC1–IAC4)                                               |       |

|     | 10.7.8 Data Address Compare Registers (DAC1–DAC2)<br>10.7.9 Data Value Compare Registers (DVC1–DVC2)   |       |

|     | 10.7.9 Data value compare Registers (DVCI-DVC2)                                                        |       |

|     | 10.7.10 Instruction Address Register (IAR)                                                             |       |

|     | 10.7.11 וואו עכווטון דומנכון דומא הפצואוידא (איזיאר איז די גער איז | . 419 |

| 10.7.12 Instruction Match Registers (IMR)                          |  |

|--------------------------------------------------------------------|--|

| 10.8 Debug configuration and control functions                     |  |

| 10.8.1 Core debug modes                                            |  |

| 10.8.2 Addtional debug functions                                   |  |

| 10.8.3 Recoverable error counter                                   |  |

| 10.8.4 PC Configuration Register 0 (PCCR0) Definition              |  |

| 10.9 Thread control and status                                     |  |

| 10.9.1 Thread control functions                                    |  |

| 10.9.1.1 Example procedure to perform instruction stepping         |  |

| 10.9.2 Thread status                                               |  |

| 10.9.3 Thread Control and Status Register (THRCTL) Definition      |  |

| 10.10 Instruction Stuffing                                         |  |

| 10.10.1 Ram registers                                              |  |

| 10.10.2 Ram instructions                                           |  |

| 10.10.2.1 Supported Ram instructions                               |  |

| 10.10.2.2 Using scratch registers as temporary storage             |  |

| 10.10.3 Ram control bits                                           |  |

| 10.10.4 Ram status bits                                            |  |

| 10.10.5 Ram data                                                   |  |

| 10.10.6 Ram Mode overview                                          |  |

| 10.10.6.1 Basic Ram process                                        |  |

| 10.10.6.2 Example Ram procedure                                    |  |

| 10.11 Direct Access to I-Cache and D-Cache Directories             |  |

| 10.11.1 General Read D-Cache Directory Sequence for L1 D-Cache     |  |

| 10.11.2 Instruction Unit Debug Register 0 (IUDBG0)                 |  |

| 10.11.3 Instruction Unit Debug Register 1 (IUDBG1)                 |  |

| 10.11.4 Instruction Unit Debug Register 2 (IUDBG2)                 |  |

| 10.11.5 Execution Unit Debug Register 0 (XUDBG0)                   |  |

| 10.11.6 Execution Unit Debug Register 1 (XUDBG1)                   |  |

| 10.11.7 Execution Unit Debug Register 2 (XUDBG2)                   |  |

| 10.12 Support for the Debugger Notify Halt (dnh) instruction       |  |

| 10.12.1 DNH Data Register (DNHDR) Definition                       |  |

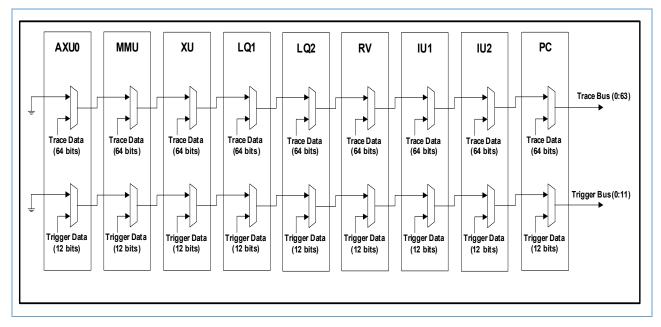

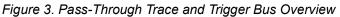

| 10.13 Trace and Trigger Bus                                        |  |

| 10.13.1 Trace and Trigger Bus Overview                             |  |

| 10.13.2 Unit Level Trace and Trigger Bus Implementation            |  |

| 10.13.3 Debug Select Registers                                     |  |

|                                                                    |  |

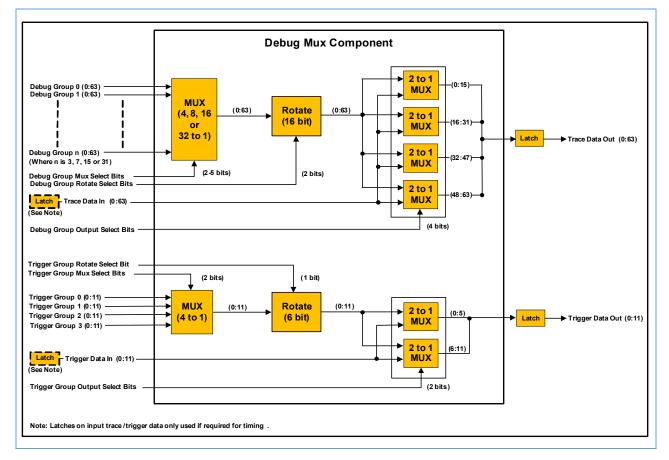

| 11. Performance Events and Event Selection                         |  |

| 11.1 Event Bus Overview                                            |  |

| 11.2 A2 Core Event Multiplexer and Performance Event Controls      |  |

| 11.2.1 Enabling performance event and trace bus latches            |  |

| 11.2.2 Performance analysis operating modes                        |  |

| 11.2.3 Options for selecting debug bus signals                     |  |

| 11.2.4 Speculative and non-speculative performance event selection |  |

| 11.2.5 Core performance event selection to external event bus      |  |

| 11.2.6 Core Event Select Registers                                 |  |

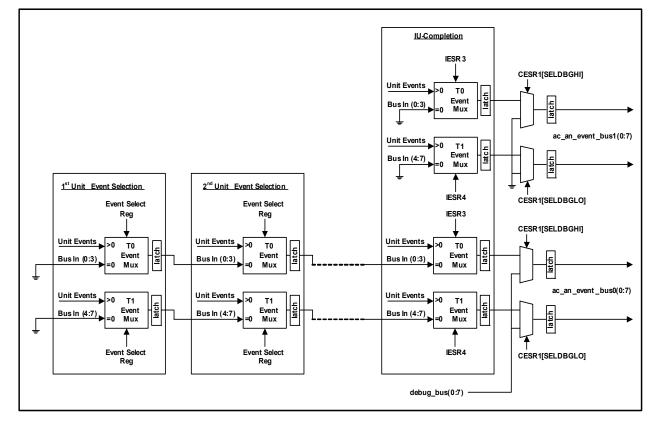

| 11.3 Unit level performance event selection                        |  |

| 11.3.1 Unit event multiplexer component                            |  |

| 11.3.2 Performance Monitor Event Tags and Count Modes              |  |

#### A20 Processor

| 11.3.3 Unit performance event tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4 Unit performance event tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 449                                                                                                                                                                           |

| 11.4.1 AXUO performance events table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                               |

| 11.4.2 IU performance events table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                               |

| 11.4.3 LQ performance events table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                               |

| 11.4.4 MMU performance events table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                               |

| 11.4.5 RV performance events table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 460                                                                                                                                                                           |

| 11.4.6 XU performance events tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 461                                                                                                                                                                           |

| 11.5 Unit event select registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 463                                                                                                                                                                           |

| 11.5.1 AXU0 event select register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 463                                                                                                                                                                           |

| 11.5.2 IU event select registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 464                                                                                                                                                                           |