You cannot select more than 25 topics

Topics must start with a letter or number, can include dashes ('-') and can be up to 35 characters long.

|

|

4 years ago | |

|---|---|---|

| custom | 4 years ago | |

| doc | 4 years ago | |

| rtl | 4 years ago | |

| LICENSE | 4 years ago | |

| readme.md | 4 years ago | |

readme.md

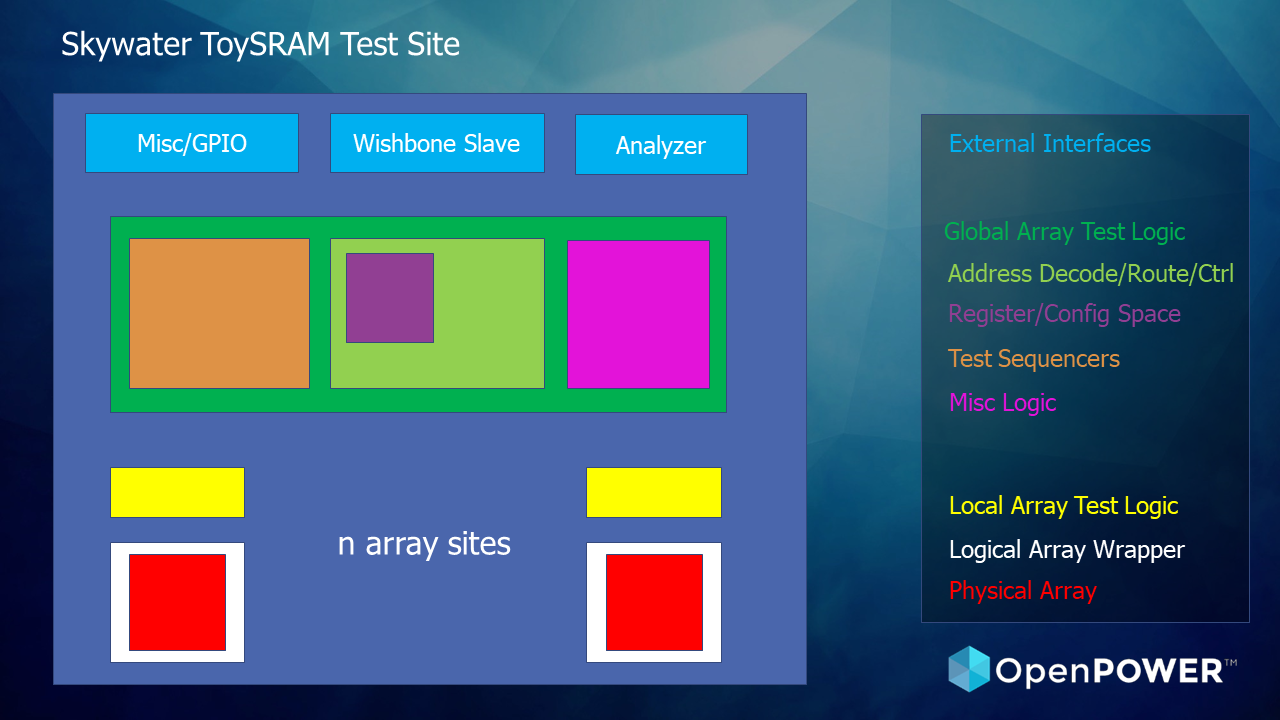

ToySRAM

A test site for a high-specific-bandwidth memory design

- We make high-specific-bandwidth multiport memories child’s play

- We make 10T SRAM a first-class citizen, and use pumping and replication for high frequency and additional ports

Description

The goal is to demonstrate specific bandwidth results from 90nm to 2nm, and use the basic design to grow as many ports as necessary through replication, to produce more efficient processors and accelerators with less circuit-design effort.

What is specific bandwidth?

- It measures the read and write bandwidth per unit area

- Bandwidth per unit area is an analog to specific gravity, which is mass per unit volume

- It's more encompassing than bit density, which drives complexity to improve bandwidth

Why does Toy-SRAM do so well?

- It's enhanced by having a 10T SRAM/2 read ports/1 write port

- It supports low-cost super-pipelining (2x+ the system frequency, without latch overhead)

- It enables energy-efficient ultralow-voltage operation by avoiding read disturb

Specific bandwidth can be expressed with two metrics:

- Technology dependent “X TB/(sec * mm 2 )”

- Technology independent “Y 1/(FO4 delay * PC PITCH * min horizontal metal pitch)”

Links

- skywater-pdk.slack.com#toysram